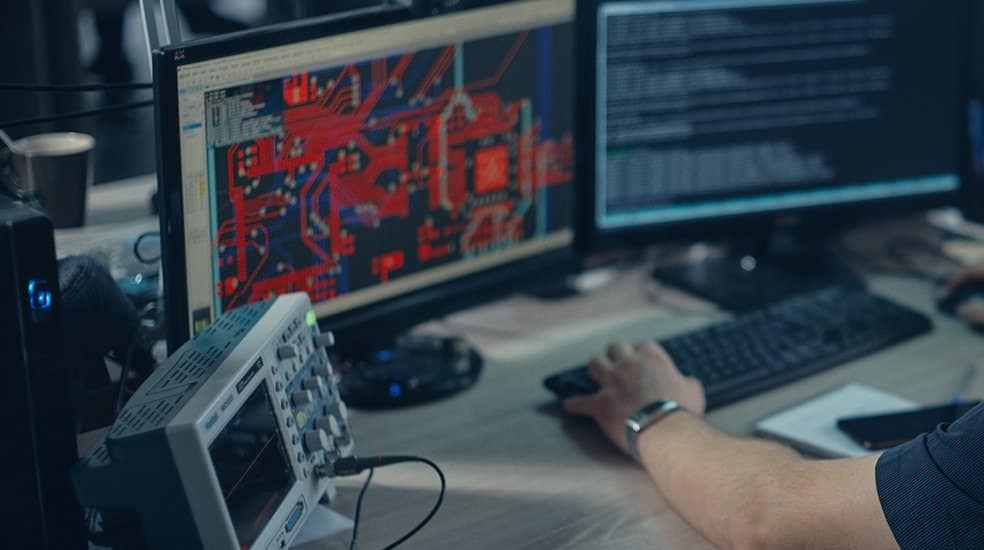

基于Hyperlynx的DDR3仿真分析过程报告

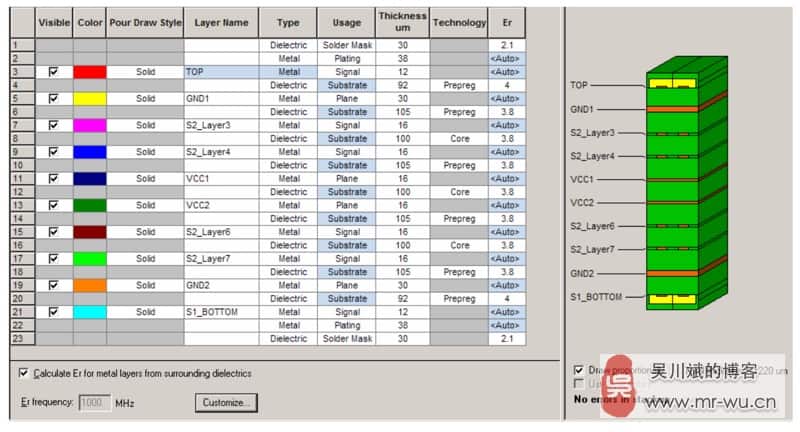

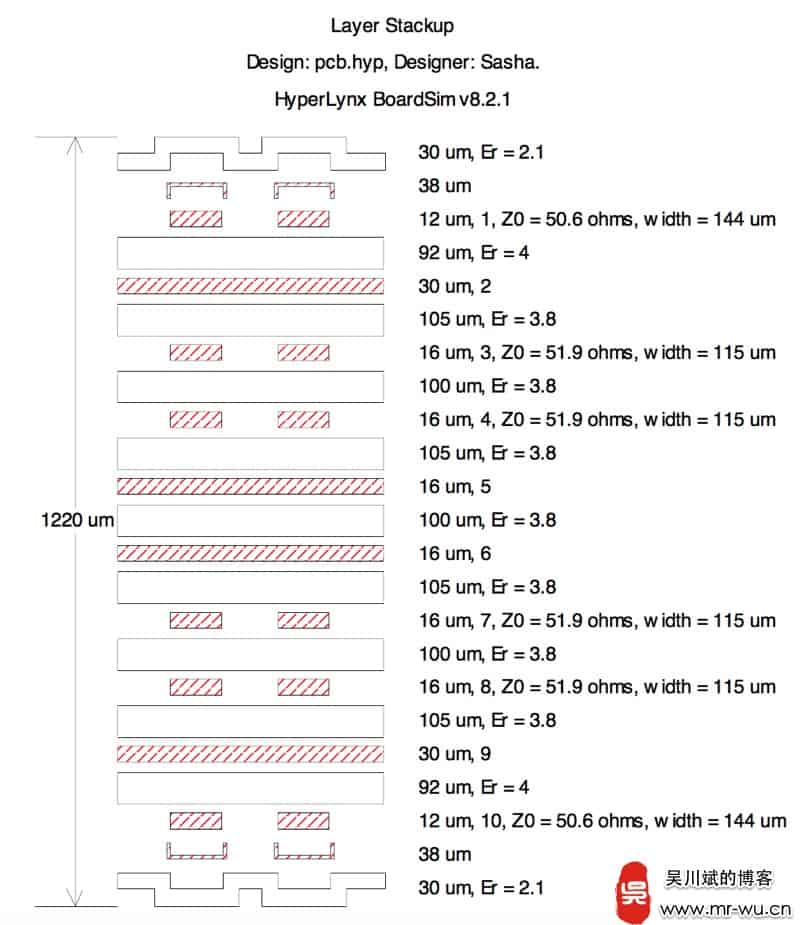

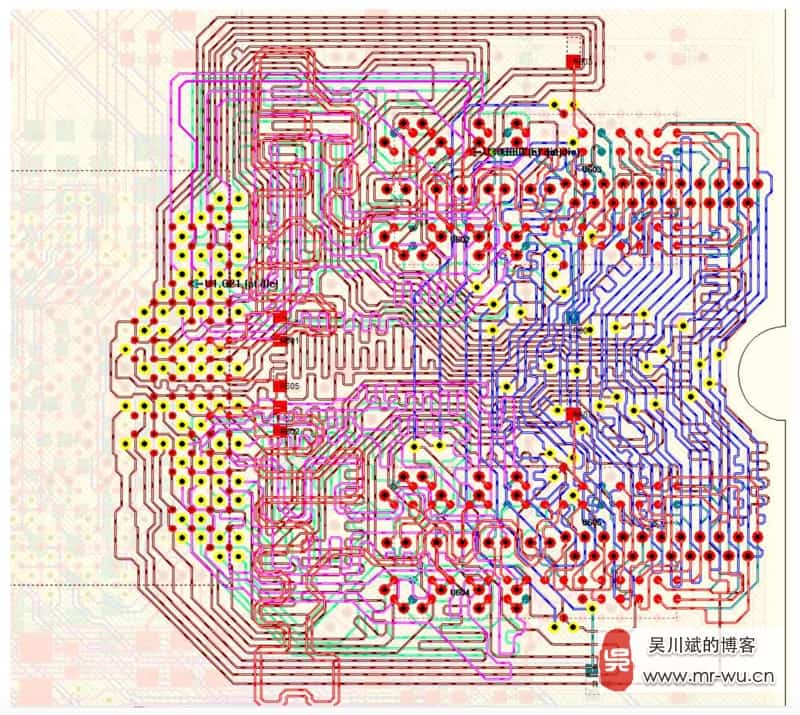

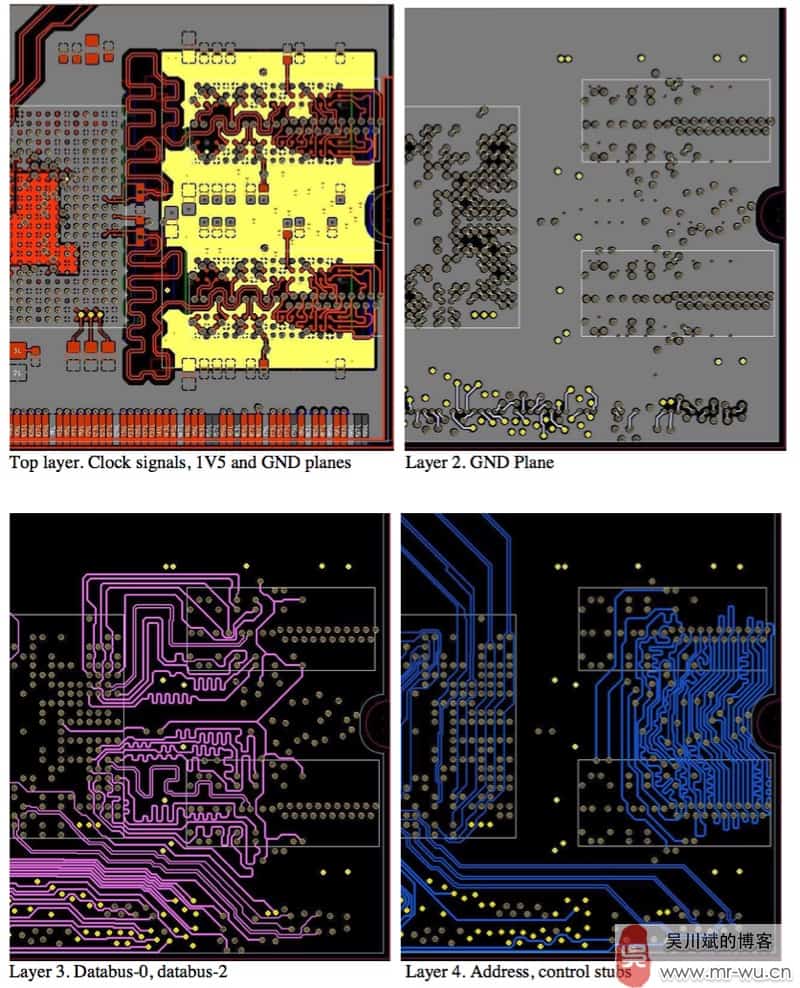

这是一篇基于Mentor公司 Hyperlynx 8.2.1 仿真软件针对 IMX53_module_v6_fdb PCB上DDR3内存布局布线的信号完整性仿真分析的过程报告。层叠结构设置,关键信号的仿真分析,有助于我们了解基于 Hyperlynx 对 DDR3 进行信号完整性仿真的整个流程。

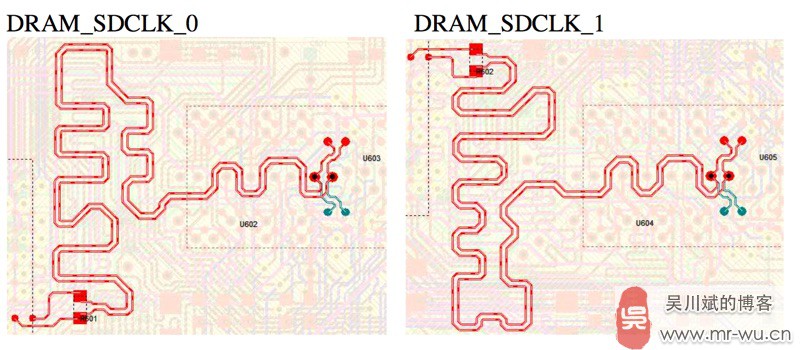

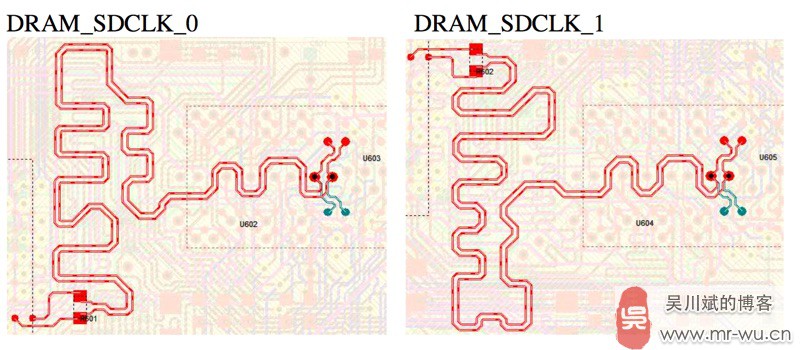

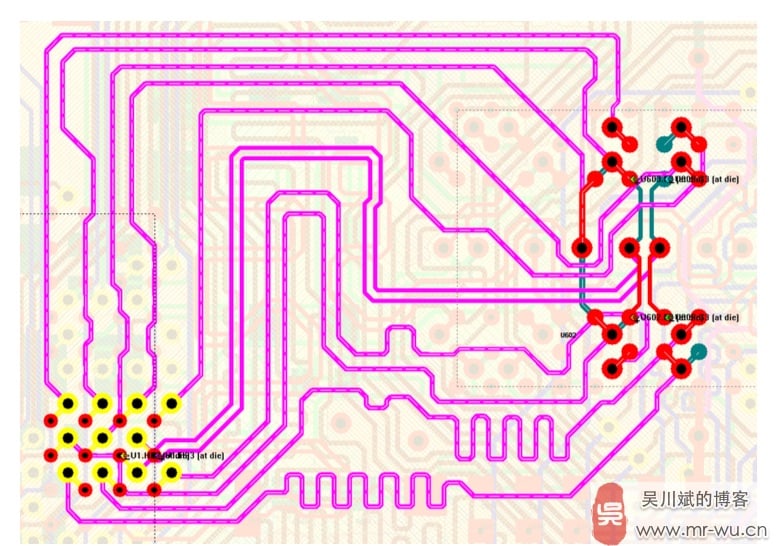

时钟差分线的端接电阻放置位置不正确,应尽量靠近接收端摆放,避免信号反射,而上图中采用靠近源端摆放。理想的情况是该端接电阻应靠近T点摆放,但因为这里采用的是DDR3内存IC顶底对贴的结构,无法实现,只能进行折中设计,在CPU U1 和 T点之间,并尽量靠近T点进行摆放。

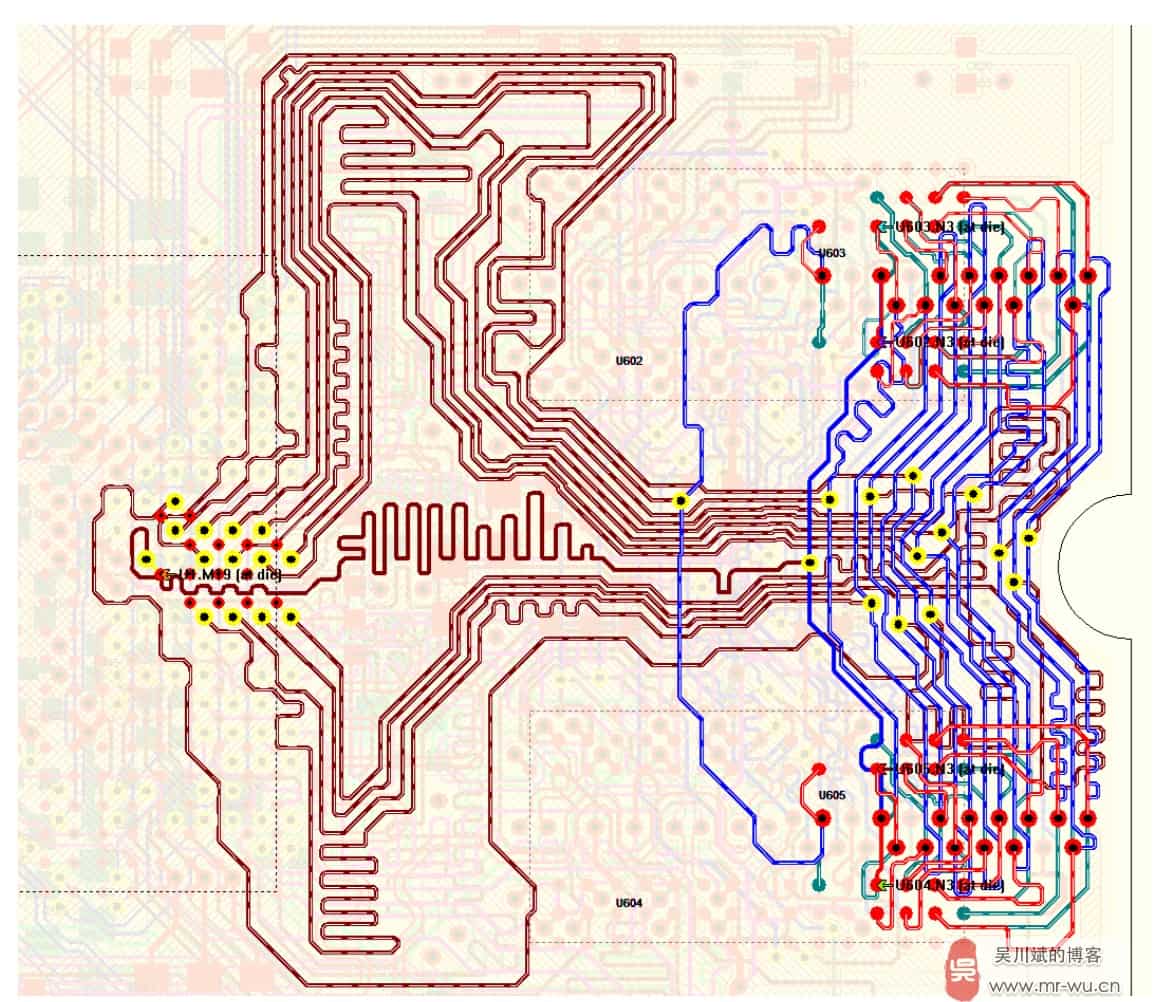

DDR3 地址线可以不同层

DDR3 数据线 同组同层

请猛击这里:DDR3 SI analisys report 百度网盘分享

4 Comments

我们做了款5G CPE,在用speedtest测试时发现速度一冲就掉网,必须重启差,而不测速是可以正常上网看视频,检查过电源,带载完全够的,5G模块通过第三方USB-5G转接板测速也是OK的,在我们的板子上却测速总是导致断网,这会是哪方面的原因导致的呢

老吴,可以把这个板子或者IBIS模型分享下吗。。。。。急需例子学习啊,谢谢

不错的DDR3仿真分析文章 国内这方面的总结资料比较少

谢谢关注