嵌入式和扇出晶圆级封装技术的发展历程 中英文版 高清电子书 Advances in embedded and fan-out wafer level packaging technologies

[视频]Sigrity如何轻松实现DDR接口精准分析而无需处理大型S参数

![[视频]Sigrity如何轻松实现DDR接口精准分析而无需处理大型S参数](https://www.mr-wu.cn/wp-content/uploads/2017/06/如何轻松实现DDR接口精准分析而无需处理大型S参数.jpg)

成功地实现DDR内存条,例如DDR4是信号完整性专家面临的最具有挑战的任务之一,在设计的早期阶段,DDR内存条往往使用理想电源环境进行分析,这样基本的信号完整性、串扰问题可以被评估和修正。但是,在验证阶段,信号完整性专家面临着重大的挑战,当使用兼顾电源影响的信号完整性分析来评估同步开关噪声(SSN)影响.为了评估同步开关噪声(SSN), 互联模型必须要考虑到:信号、电源、接地结构以及其间的耦合。

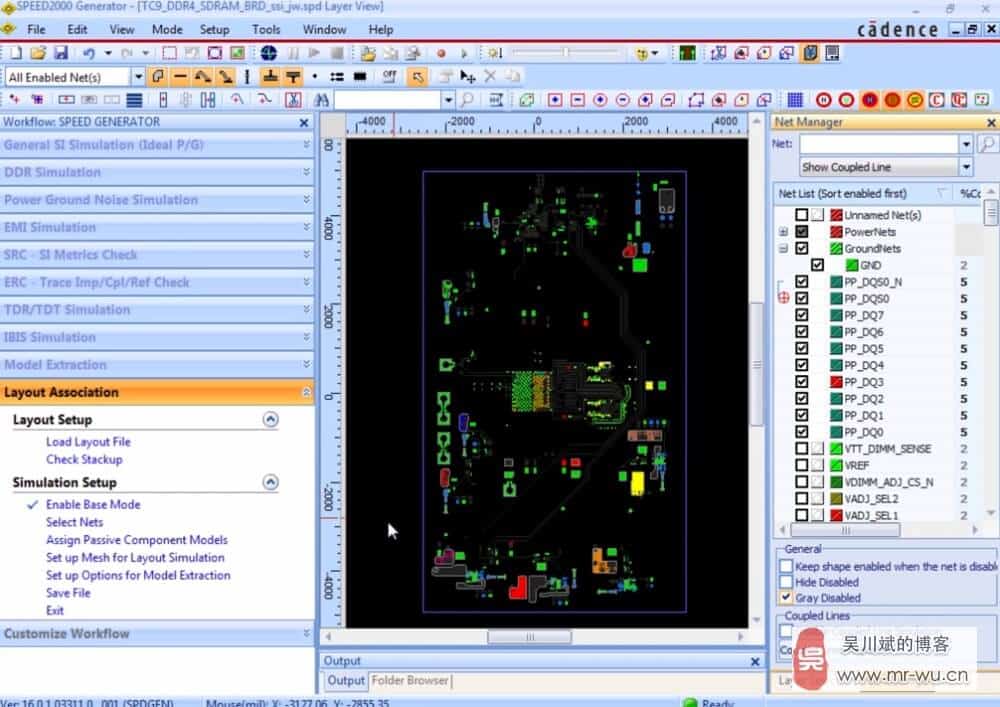

混合或者全波三维场求解器,常被用于提取PCB设计的S参数模型,可是,大型DDR内存条的S参数在很多电路仿真器中无法很好的仿真。这导致仿真结果存在收敛性和稳定性方面的问题。为了解决这个问题,可以执行更进一步的操作,将S参数模型转换成较为简单的宽频Spice模型。但是这种转换常常需要修正模型的无源性和因果性问题。导致信号完整性专家质疑他们的同步开关噪声(SSN)仿真的准确性。为解决以上问题,Cadence Sigrity 技术为信号完整性工程师提供了一个全新的替代方案:FDTD direct 仿真方法学。

通过Sigrity独特的混合求解器以及时域有限差分(FDTD)引擎,直接对PCB和IC封装几何结构进行求解,并执行兼顾电源的时域信号完整性分析,而无需S参数模型。信号完整性工程师可以自信地、准确地执行信号完整性详尽分析,包括对同步开关噪声(SSN)影响的评估,而无需处理大型、复杂的S参数。拥有了准确、清晰的同步开关噪声仿真结果,信号完整性工程师在验证DDR时将会极有信心,其仿真结果会与实验室测试结果一致,而这将帮助缩短设计周期,让你的产品及时上市。

老wu这里分享的视频将会演示如何使用Allegro Sigrity SI Base以及具有电源意识的Power-Aware SI Option来进行仿真。

1 Comment

老吴,站内的老视频基本上用adobe的都看不了了,能否帮忙更新下,谢谢啦