一图弄懂半导体–台积电与英特尔在追赶的纳米制程是什么?

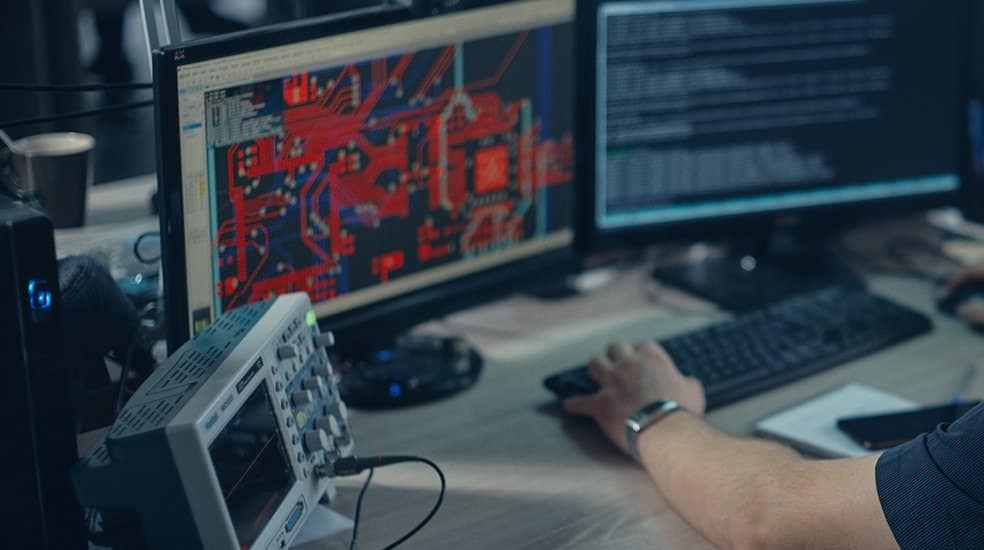

制程工艺就是通常我们所说的CPU的「制作工艺」,是指在生产CPU过程中,集成电路的精细度,也就是说精度越高,生产工艺越先进。在同样的材料中可以制造更多的电子元件,连接线也越细,精细度就越高,CPU的功耗也就越小。

制程工艺的微米是指IC内电路与电路之间的距离。制程工艺的趋势是向密集度愈高的方向发展。密度愈高的IC电路设计,意味着在同样大小面积的IC中,可以拥有密度更高、功能更复杂的电路设计。微电子技术的发展与进步,主要是靠工艺技术的不断改进,使得器件的特征尺寸不断缩小,从而集成度不断提高,功耗降低,器件性能得到提高。晶元制造工艺在1995年以后,从0.5微米、0.35微米、0.25微米、0.18微米、0.15微米、0.13微米、90纳米、65纳米、45纳米、32纳米一直发展到目前最新的10纳米,而7纳米制程工艺将是下一代CPU的发展目标。

计算公式:以当前处理器的制程工艺乘以0.714即可得出下一代CPU的制程工艺,如90*0.714=64.26,即65纳米。

提高处理器的制造工艺具有重大的意义,因为更先进的制造工艺会在CPU内部集成更多的晶体管,使处理器实现更多的功能和更高的性能;更先进的制造工艺会使处理器的核心面积进一步减小,也就是说在相同面积的晶圆上可以制造出更多的CPU产品,直接降低了CPU的产品成本,从而最终会降低CPU的销售价格使广大消费者得利;更先进的制造工艺还会减少处理器的功耗,从而减少其发热量,解决处理器性能提升的障碍,处理器自身的发展历史也充分的说明了这一点,先进的制造工艺使CPU的性能和功能一直增强,而价格则一直下滑,也使得电脑从以前大多数人可望而不可及的奢侈品变成了现在所有人的日常消费品和生活必需品。

总体来说,更先进的制成工艺需要更久的研制时间和更高的研制技术,但是更先进的制成工艺可以更好的提高中央处理器的性能,并降低处理器的功耗,另外还可以节省处理器的生产成本,以便降低售价。cpu的制程工艺,从14nm起,进展变得非常缓慢,摩尔定律已经失效了。因为电子隧道效应的存在,公认的晶体管制程极限是5nm。

根据量子力学计算,硅芯片中线宽低于10nm左右的时候,电子的量子隧道效应将占据主要地位,电子不再沿着预先设计好的电路运行,而是任意穿过10nm以下的绝缘壁。因此目前预计可能的线宽极限是1~10nm,不会低于一纳米。

芯片商最关心的可能就是成本问题了,“摩尔定律的终结不是技术问题,而是经济问题。” 鲍特姆斯说,包括英特尔在内的一些公司,依然试图在达到量子效应之前继续缩小元件体积,但是,产品缩得越小,成本越高。每次产品体积缩小一半,生产商就需要全新的更准确的影印石版机器。如今,建立一条全新的生产线往往需要投入几十亿美元,这个成本仅有少数几家厂商可以承受。而由移动设备带来的市场碎片化,使得筹集这样的资金更加困难。“一旦下一代的每晶体管成本超过现有的成本,产品更新就会停止。”很多业内人士认为,半导体行业已经非常接近这个“产品更新停止”的阶段。

1 Comment

值得思考哦,受教了!